Tanner Tools 2019功能强大的电路设计软件,适用于集成电路(IC)、模拟/混合信号(AMS)和MEMS设计。2019版本进行了全面升级和优化,提供了紧密集成的混合信号设计套件,设计周期极短、性价比高,特别适合物联网和基于项目的设计,以一种高度集成的端到端流程支持进行快速的电路设计、模拟和混合信号IC、MEMS和光子设计等。这里带来的是破解版,下面有着详细的破解教程。

软件特色

1、继承的连接

S-Edit现在提供对通过参数化电源/接地符号或网络标签定义的继承连接的支持。

2、符号和示意图中的图像

现在可以在符号视图和示意图视图中插入图像。这可以用于创建更详细的符号,也可以用于在示意图中添加注释或文档。 Windows®支持位图和矢量格式。 Linux仅支持位图格式。

3、AFS和EZWave集成

S-Edit现在与AFS,Eldo和EZwave集成在一起,以在整个Linux环境中提供仿真设置,启动,交叉探测和向后注释支持。 Windows上的SEdit和Linux上使用PSF输出格式的AFS / EZWave现在也支持设置和启动,交叉探测和向后注释。反向注释支持包括DC OP V / I,AC小信号,模型参数,设备AC小信号参数表和设备参数反向注释。

4、布局伪造

Layout Forge是一种生产力增强工具,适用于模拟布局设计人员执行设备级别的布局和布线,从而可以完全控制布局和布线。 Layout Forge在原理图中识别差分对,电流镜和共源共栅电流镜,并自动在布局中生成放置和布线的单元。设计人员可以在瞬间中心的帮助下自定义设备的放置,并可以自定义工艺路线。

5、邻接

参数化的单元邻接可以允许参数化的单元实例在邻接时调整其几何形状以占据最小面积。例如,如果一个n沟道MOSFET的两个实例共享相同的源极或漏极,则基台将重新生成实例,以去除额外的触点并使这两个器件彼此非常靠近。基台将检查有效的连接,相同类型或类别的设备,并确保LVS清洁结果。必须由PDK中的铸造厂启用参数化的单元桥台。

安装方法

1、下载安装包,解压缩并运行安装,选择安装产品

2、选择软件安装位置

3、选择需要安装的产品,自行勾选即可

4、阅读软件许可协议,点击同意

5、一切准备就绪,点击安装

6、正在安装中,请耐心等待一会

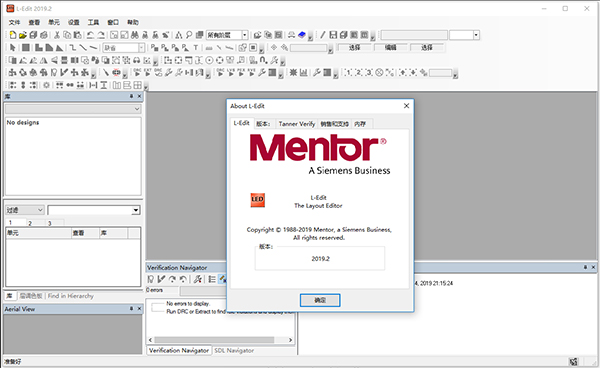

7、安装成功,退出安装向导

8、右键管理员身份运行MentorKG.exe,会自动生成LICENSE.TXT,保存在一个指定位置,比如安装目录下

9、右键我的电脑——>属性——>高级系统设置——>环境变量,创建系统环境变量

变量名:LM_LICENSE_FILE

变量值:指向LICENSE.TXT路径

10、运行软件即可免费使用了

软件功能

1、完整的IC设计捕捉环境

Tanner S-Edit是一个易于使用的设计环境,用于原理图捕获和设计输入。 它为您提供了处理最复杂的混合信号IC设计捕获所需的功能。 S-Edit与Tanner T-Spice,Analog FastSPICE™(AFS)或Eldo®仿真器,Tanner L-Edit IC布局工具以及Calibre®LVS和PEX工具紧密集成。 S-Edit通过优化您的生产率并加快将概念应用于硅的速度,可以帮助您满足当今快速发展的市场的需求。 更快的设计周期为您提供了向最佳解决方案过渡的更多灵活性,从而节省了更多时间和资源来进行工艺角确认。 结果是减少了下游风险,提高了产量并缩短了上市时间。

2、最复杂的混合信号IC设计的原理图捕获

总线支持加快了混合信号设计的创建

先进的阵列支持可轻松创建和编辑具有重复块的存储器,图像或电路

具有快速固定(热点)功能的橡皮筋连通性编辑功能可加快设计修改速度

S-Edit在设计过程中实时显示评估的参数; 可以显示或评估具有基于其他电路参数的公式的参数

自动生成符号使您可以轻松地从原理图创建符号并同步所有更改

所有操作均可通过TCL / Tk命令语言完全编写脚本

可记录的脚本使您能够自动化任务或扩展工具以满足特定于应用程序的需求

可重播的日志可在网络或硬件出现意外故障时进行恢复

S-Edit在突出显示层次结构时执行网络突出显示并保持网络突出显示

口径RVE在原理图,布局和LVS报告之间进行交叉探测以突出显示网络或设备

原理图ERC使您可以检查设计中是否存在常见错误,例如未驱动的网络,未连接的引脚以及由多个输出驱动的网络。 设计检查是完全可配置的,包括自定义验证脚本

3、与仿真紧密集成

从原理图捕获环境中驱动模拟器。 这样就可以直接在原理图上查看工作点结果,查看设备的小信号参数,查看模型参数以及执行波形交叉探测以查看节点电压以及设备端子电流或电荷。

S-Edit为电路设计,仿真,分析和调整的迭代循环创建了高效流程。 专注于设计而不是数据处理,从而加快了设计过程。

4、与第三方工具和旧版数据轻松互操作

S-Edit从第三方工具中以本机OpenAccess或EDIF进行读取,并自动转换原理图和属性以无缝集成遗留数据

网表可以以灵活的,用户可配置的格式导出,包括SPICE和CDL变体,EDIF,结构性Verilog 以及结构化的VHDL

S-Edit中的库支持最大限度地重用了以前项目中开发的或从第三方供应商处导入的IP

5、强大且易于使用的界面

S-Edit使前端设计的捕获更轻松,更高效

完全由用户可编程的设计环境使您可以重新映射热键,创建新的工具栏以及根据自己的喜好自定义视图-所有这些都在简化的GUI中

完整的用户界面 支持多种语言,包括英语,日语,简体中文和繁体中文

S-Edit提供Unicode支持; 所有用户数据都可以输入国际字符集。ird-PartyTools and Legacy Data

S-Edit从第三方工具中以本机OpenAccess或EDIF进行读取,并自动转换原理图和属性以无缝集成遗留数据

网表可以以灵活的,用户可配置的格式导出,包括SPICE和CDL变体,EDIF,结构性Verilog 以及结构化的VHDL

S-Edit中的库支持最大限度地重用了以前项目中开发的或从第三方供应商处导入的IP

6、具有成本效益

S-Edit提供了理想的性能成本比,使您可以最大化项目中的设计人员人数

由于S-Edit在Windows®和Linux平台上运行,因此设计人员可以在具有成本效益的工作站或 笔记本电脑 这意味着您可以随身携带您的工作,甚至在家中,也可以继续工作,以满足上市时间的压力

提供两种配置:完整的原理图编辑器和原理图查看器

标签: 电路设计

电路的设计在生产中是很关键的,电路设计仿真软件在电子工程和电子学教育中扮演着至关重要的角色,它们帮助工程师和学生通过模拟电路的实际工作状态来验证设计的正确性。

精品推荐

-

Altium Designer10破解工具

详情 -

MasterCAM X9注册机

详情 -

Altium Designer绿色版

详情 -

MasterCAM9.1汉化版

详情 -

Master Cam 2020

详情 -

Master Cam 2017完整汉化包

详情 -

Multisim14元件库大全

详情 -

Proteus仿真软件

详情 -

奎享雕刻

详情 -

AD17.0.6破解版

详情 -

Cimatron e11

详情 -

MasterCAM X9免F8绿色版

详情 -

英科宇机械工程师CAD2020

详情 -

斯沃数控机床仿真软件破解版

详情 -

Altium Designer15注册机

详情 -

Mentor Pads完整破解版

详情

-

8 AD16破解文件

装机必备软件

网友评论